# **MART1700:**

TEST MODULE TO RECORD AND PLAYBACK AUDIO MESSAGES

USING ISD1700 IC SERIES

#### 1. CONSTRUCTION OF THE MODULE

**MART1700** is a module designed to record and playback multi audio signals (multi messages) using ISD1700 series integrated circuits of the American firm *Winbond Electronics Corporation America (WECA)*. Messages are stored in non-volatile memories made in unique Multilevel Storage Technology (MLS) featuring high quality audio recording, simplicity of operation and long-term retention of recording after switching off power (100 years). The device operates in dual mode: standalone mode (through pushbutton interface) or SPI mode (through 4-wire serial interface SPI). It enables simple realization of functions without the need for additional control circuits.

In standalone mode, the following functions are realized:

- · level-triggered consecutive recording of messages

- · edge-triggered playback of individual messages,

- · level-triggered looping of playback messages,

- · audio playback speed change,

- · erasing the first or last message,

- level-triggered global erasing of all messages (whole memory),

- · edge-triggered jump to the next message in memory (message cueing),

- · 8-level volume control on speaker outputs,

- · signalling the ready state of device,

- resetting the device to default state.

In SPI mode, the device executes commands similar to the push-button controls, plus the following commands:

- analog path configuration (APC) inside the device,

- direct memory addressing to specify the start and end addresses of record, playback and erase operations.

Current state of the chip (operation in progress) is indicated by LED1 and LED2 indicators. At the end of each operation ISD1700 devices automatically enter into standby (power-down) mode, drawing current <1 µA.

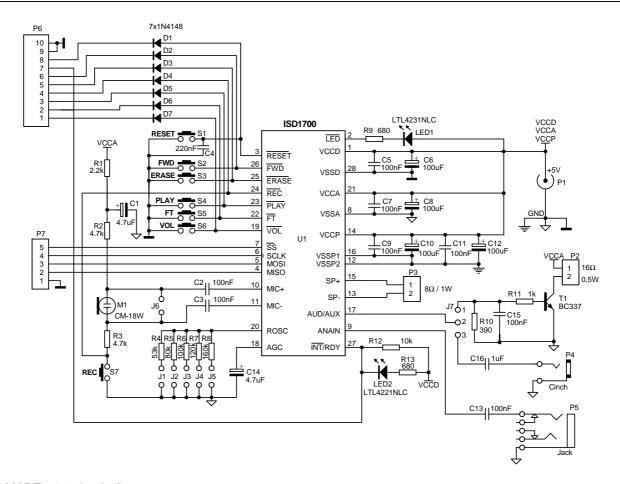

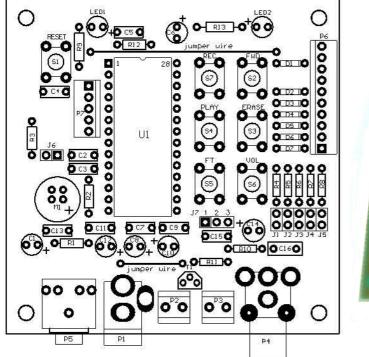

Fig. 1 shows the circuit diagram of MART1700 module and Fig. 2 its PCB component layout. The following external components are required for proper operation of the module:

- stabilized power supply unit of voltage range +2.4 ... +5.5 V, connected to socket P1,

- $1W/8\Omega$  speaker connected to terminal strip P3 or  $0.5W/16\Omega$  speaker connected to terminal strip P2.

- optionally, source of sound signal (PC sound card, tape recorder, CD player, etc.), connected to socket P5.

Fig.1. MART1700 circuit diagram.

Fig. 2. MART1700 component layout (scale 1.2:1).

#### 2. MODULE PORTS

The module contains mechanical components (switches S1...S7, jumpers J1...J7, input and output sockets P4, speaker sockets P2 and P3) essential for realization all the device functions in standalone mode. Moreover, input pins of control signals for actuating individual functions are additionally connected to plug P6, parallel to corresponding switches S1...S7. In this way, it is possible to actuate individual functions both by means of switches as well as external signals of appropriate logical levels. Moreover, SPI interface lines are fed to plug P7 which enables the use of, for example, microcontroller for control.

Messages are recorded into the system through microphone provided in the module or from external source (tape recorder, CD player, computer sound card, etc.) through socket P5. Message playback is led to PWM type speaker outputs to which a speaker can be directly connected through socket P3. Simultaneously, the message is output either as an unamplified analog audio signal to socket P4 or after amplification to the speaker connected to socket P2 (depending on jumper J7).

The module is designed for supply with stabilized voltage in the range  $V_{CC} = 2.4 \dots 5.5 \text{ V}$  led to socket P1.

All control signals RESET, FWD, ERASE, REC, PLAY, FT, VOL and INT/RDY as well as SPI interface signals SS, SCLK, MOSI and MISO of ISD1700 are digital signals accepting one of two possible voltages: low (logical L level) or high (logical H level), dependent on the power supply voltage Vcc. In case of ISD1700 series circuits, these voltages have following values with respect to ground:

- input low voltage: -0.3 V ... 0.3xVcc,

- input high voltage: 0.7xVcc ... Vcc,

- output low voltage: -0.3 V ... 0.3xVcc, max. 4 mA,

- output high voltage: 0.7xVcc ... Vcc, max. 1.6 mA.

Hereinafter, an alternative notation will be used for the state of a specific control signal (input/output): signal name = L, H, LH, HL, where: LH – rising edge and HL – falling edge, of the signal.

Control inputs  $\overline{\text{RESET}}$ ,  $\overline{\text{FWD}}$ ,  $\overline{\text{ERASE}}$ ,  $\overline{\text{REC}}$ ,  $\overline{\text{PLAY}}$ ,  $\overline{\text{FT}}$ ,  $\overline{\text{VOL}}$ , MOSI, SCLK and  $\overline{\text{SS}}$  have internal pull-up resistors and forced H level on these pins. Additionally, inputs  $\overline{\text{FWD}}$ ,  $\overline{\text{ERASE}}$ ,  $\overline{\text{REC}}$ ,  $\overline{\text{PLAY}}$ ,  $\overline{\text{FT}}$  and  $\overline{\text{VOL}}$  have internal debounce circuits. Active state of these signals is L level.

- S1 the push-button for triggering RESET function (input of RESET signal) device enters into the initial state and initializes all pointers to the default state without erasing recorded messages.

- S2 the push-button for triggering FWD function (input of  $\overline{\text{FWD}}$  signal) forward operation, advance to the next message. Short L pulse causes:

- in standby mode advance from current message to the next message (one message forward) and setting the playback pointer on it,

- during playback halting this process, advancing to the next message and restarting playback from the beginning.

- S3 the push-button for triggering ERASE function (input of ERASE signal) erasing the first or last message in memory or global erasing of all messages (whole memory).

Short L pulse erases the current message (indicated by internal playback pointer) but only if it is either the first or last message. Holding this input at L for more than 3 seconds initiates the global erase operation.

- S4 the push-button for triggering PLAY function (input of PLAY signal) playback of current message in memory.

- Beginning of the current message is determined by the internal playback pointer. Short L pulse starts playback of this message and the next pulse L stops this operation. Playback also stops automatically when end of message is reached (internal EOM marker). For such operation, it is required that duration of pulse L is shorter than duration of message playback.

- In case  $\overline{PLAY}$  signal is held constantly in L state, the system plays back consecutive messages recorded in memory. Return of signal to H halts playback after encountering end of current message. From this moment, this message becomes the current message.

- S5 the pushbutton for triggering FT function (input of FT signal) in standalone mode, it configures the analog path as the feed-through path from ANAIN audio input (socket P5) to SP+/- and AUD/AUX outputs.

- In SPI mode the above configuration is controlled by internal Analog Path Configuration (APC) register of the chip.

- S6 the pushbutton for triggering VOL function (input of VOL signal) ) control of audio volume on speaker outputs SP+/- (P3) and AUD/AUX (P2 or P4). There are 8 steps of volume control. The default value (after power-on) is maximum. Repeated L pulses decrease volume level by 1 step until minimum value is reached and then increase volume level by 1 step until maximum value is reached, and so on.

- S7 the push-button for triggering REC function (input of REC signal) level-activated recording of message.

Recording is initialized by HL edge of this signal, continues when it stays at L and stops when LH edge occurs or the memory is full. In standalone mode, messages are recorded sequentially until end of memory. The location where recording of individual message starts is determined by the internal record pointer. Addressable record and playback operations are accessible only in SPI mode.

Pressing any pushbutton S1...S7 forces the logical L level on suitable control pin of ISD1700.

- P1 2.1/5.5 standard DC power supply socket stabilized supply voltage in the range of 2.4...5.5 V.

- P2 terminal strip for  $16\Omega$  / 0.5W speaker connection analog audio signal AUD amplifier output.

- P3 terminal strip for  $8\Omega/1W$  speaker connection direct PWM outputs provide differential complementary speaker signals SP+ and SP- .

- P4 cinch socket for the analog audio output signal AUX.

- P5 mono Jack (socket) for audio input signal from external source.

- P6 control connector whose individual pins are connected in parallel with corresponding function switches S1...S7:

- P6/1 input of VOL signal (connected with S6).

- P6/2 input of FT signal (connected with S5).

- P6/3 input of PLAY signal (connected with S4).

- P6/4 input of REC signal (connected with S7).

- P6/5 input of ERASE signal (connected with S3).

- P6/6 input of FWD signal (connected with S2).

- P6/7 the "open drain" outputs one of two signals:

- in standalone mode ready signal (RDY) which stays L during record, playback, erase and forward operations, and stays H in power-down state,

- in SPI mode interrupt signal (INT) after completing the SPI command (L level).

- P6/8 input of RESET signal (connected with S1).

- P6/9 digital ground, (-) supply.

- P6/10 digital ground, (-) supply.

- P7 SPI interface plug:

- P7/1 digital ground, (-) supply.

- P7/2 MISO (Master In Slave Out) output line, data is clocked out on the HL edge of the SCLK signal. When SPI is inactive (SS = H), it is tri-state.

- P7/3 MISO (Master In Slave Out) input line, data is clocked into the device on the LH edge of the SCLK signal.

- P7/4 input of clock signal SCLK.

- P7/5 input of SS signal which activates SPI interface in Slave mode.

- J1...J5 jumpers for programming the sampling frequency (and hence the upper cut-off frequency) of recorded signal and its playback speed change. Specific sampling frequency is obtained by shorting relevant jumper with other jumpers open. Depending on selected sampling frequency, corresponding record duration is obtained as available in given version of ISD1700. Approximate values of such durations are presented in Table 1 below.

Table 1

|    | Sampling<br>frequency<br>[kHz] |     | Max. record duration [s] |         |         |         |         |          |          |          |          |          |

|----|--------------------------------|-----|--------------------------|---------|---------|---------|---------|----------|----------|----------|----------|----------|

|    |                                |     | ISD1730                  | ISD1740 | ISD1750 | ISD1760 | ISD1790 | ISD17120 | ISD17150 | ISD17180 | ISD17210 | ISD17240 |

| J1 | 12                             | 5.1 | 20                       | 26      | 33      | 40      | 60      | 80       | 100      | 120      | 140      | 160      |

| J2 | 8                              | 3.4 | 30                       | 40      | 50      | 60      | 90      | 120      | 150      | 180      | 210      | 240      |

| J3 | 6.4                            | 2.7 | 37                       | 50      | 62      | 75      | 112     | 150      | 187      | 225      | 262      | 300      |

| J4 | 5.3                            | 2.2 | 45                       | 60      | 75      | 90      | 135     | 181      | 226      | 271      | 317      | 362      |

| J5 | 4                              | 1.7 | 60                       | 80      | 100     | 120     | 180     | 240      | 300      | 360      | 420      | 480      |

- J6 the jumper for switching the microphone signal off while recording sound signal from an external source:

- closed the microphone is switched off,

- open the microphone is switched on.

- J7 the jumper for switching the kind of analog audio signal output:

- 1-2 closed amplified analog audio signal AUD is fed to the speaker connected to terminal strip P2,

- 2-3 closed analog audio signal AUX is fed to P4 socket.

Note: AUD/AUX is either an AUD or AUX signal output (default AUD, switching is possible only in SPI mode). AUD is a current signal, AUX is a voltage signal.

- LED1 the LED for indicating the kind and state of operation in progress:

- turned on record operation,

- blinks playback, forward and erase operations and signalling of memory error (blinking mode depends on kind of operation).

LED2 - the LED for indicating the ready state or interrupt signal INT:

- turned on activity state, any function in progress,

- turned off power-down state.

#### 3. PRINCIPLE OF OPERATION

ISD1700 enables recording sound into internal non-volatile memory. It is possible to record 4 so-called Sound Effects (SE) and specific number of independent audio messages.

The module is provided with pushbuttons S1...S7 to force logical L state on individual control pins and to simultaneously actuate the corresponding system function available in standalone mode. Instead of these pushbuttons, external control signals of appropriate logical values L or H fed to socket P6 can also be used for control. Full control of circuits is obtained in SPI mode through SPI interface signals fed to socket P7.

For simplification, in further description of individual module functions, it is assumed that control is performed by means of the pushbuttons.

Memory area is divided into rows forming the smallest addressable units of memory determining storage resolution. Access to memory depends on operating mode. In standalone (pushbutton) mode, access is automatic through internal management system without the possibility of addressing memory. In SPI mode, full addressing of memory is possible by means of 11-bit address sent by MOSI line.

Storage resolution, i.e. record duration of a single row of memory (i.e. the shortest message) depends on the sampling frequency – Table 2.

Table 2

| Sampling frequency<br>[kHz] | 12   | 8   | 6.4 | 5.3 | 4   |

|-----------------------------|------|-----|-----|-----|-----|

| Record resolution [ms]      | 83.3 | 125 | 156 | 188 | 250 |

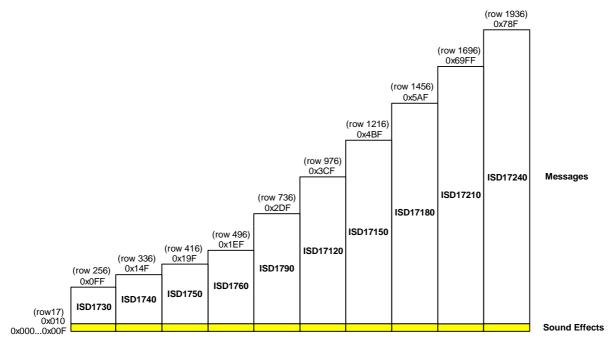

Individual ISD1700 series circuits have different memory sizes, relevant number of addressable rows, and hence different total recording times at specific sampling frequency – Table 1. Fig. 3 presents memory addressing ranges for the individual circuits.

For the 4 sound effects, the first 16 rows of memory of addresses 0x000h...0x00Fh have been reserved whereby each effect occupies 4 rows of memory. The remaining memory, that is from address 0x010h right up to the end is assigned for recording audio messages (hereinafter, the letter "h" in hexadecimal notation will be omitted).

Fig. 3. ISD1700 memory organization.

Operation of circuits depends on the operating mode. In standalone (pushbutton) mode, control occurs through corresponding change of logical state on RESET, FWD, ERASE, REC, PLAY, FT, VOL control pins. During this time, SPI interface should be off (P7/5 unconnected, viz. P7/5=H). In this mode, the device utilizes the mechanism of automatic internal connections configuration for the audio signal depending on the function realized and utilizes the built-in circular memory management protocol.

In standalone mode, the device realizes sequential (address-free) recording of messages (REC), playback (PLAY), erasing (ERASE) and jumping over messages (FWD). While recording, consecutive messages are recorded one after the other without the need to specify their addresses. Each message occupies at least 1 row of memory and hence the maximum number of independent messages that can be recorded in this way, equal to the number of memory rows, depends on the type of device used (Fig. 3). Similarly, 4 independent sound effects can be recorded.

Circular memory management protocol controls layout of messages recorded, their erasure and playback. For this purpose, 3 internal memory pointers are utilized:

- record pointer indicates the place from which the next recording will start (first line of memory after last message recorded or first line in place of last message erased),

- playback pointer indicates first line of current message for playback (last recorded or indicated after forward function FWD),

- erase pointer operates synchronously with playback pointer and signals the possibility of erasing the given message (it must be the first or last in memory).

Before executing any function connected with access to memory, the protocol checks current memory structure regarding conformity with the protocol. In case non-conformity is detected, LED1 blinks 7 times and the device stops performing its functions with the exception of clearing and global erase. The only way for getting out of this state is global erase. For this purpose, press and hold ERASE button for specific time. LED1 will blink 7 times after which whole memory content is erased. This time depends on sampling frequency and for frequency of 8 kHz, it is about 12 seconds. In case of other sampling frequencies, the time will be correspondingly longer or shorter.

Circular memory management protocol operates only in the area in which messages are recorded, viz. from address 0x010 to end of memory, whereas it does not function in the area of sound effects.

Instead of pushbuttons S1...S7 for control, it is also possible to utilize external control signals of appropriate logical level fed to socket P6.

In SPI mode, control occurs through a 4-wire serial interface. Instructions analogical to control functions are realized in standalone mode and there is also the facility of modifying internal links for audio signal (analog path configuration) as well as facility of audio memory internal addressing for performing the addressed record and playback. More information on this mode is available in Chapter 5.

Analog path configuration defining the mode of operation is recorded in the internal register of APC and its content can only be read and modified in SPI mode. Initial value of register is entered into it automatically from the non-volatile memory having factory settings. This always occurs after switching on supply or after realization of RESET function. Factory settings are as follows:

- · recording signal from microphone input MIC,

- function FT operates to signal from audio input ANAIN (socket P5),

- · playback only of signal recorded in memory,

- · access switched on to sound effects SE,

- · maximum playback volume,

- PWM speaker outputs as well as analog audio AUD current outputs switched on.

# 4. STANDALONE (PUSH-BUTTON) MODE OPERATIONS

In this operating mode, individual device functions are triggered through built-in pushbuttons S1...S7 whose actuation causes logical state L to be forced onto corresponding control pin of ISD1700. Interface SPI should be disabled, viz. H state to occur on socket P1/5 terminal, obtained with unconnected input (due to internal pull-up resistor).

After power is applied, the reset operation is automatically performed and record and playback pointers are initialized as follows:

- if no messages are present inside the memory both pointers indicate the beginning of memory area assigned for message recording, i.e. the beginning of 17-th row.

- if messages are present the record pointer indicates the next available memory row following the last message in memory and the playback pointer indicates the beginning of the last recorded message.

After each record operation, the record pointer indicates the next available memory row; however the current position of playback pointer is affected either by the record or forward operation.

Above comments refer only to the memory area designated for messages, however in case of sound effects (SE), the rules described below apply.

#### 4.1. Sound Effects (SE)

The first sixteen memory rows are reserved for Sound Effects which can be achieved by several control pins. There are four special sound effects marked as SE1, SE2, SE3 and SE4. Each SE occupies four designated memory rows. They are recorded sequentially in memory and the duration of each of them depends on the sampling frequency, according to Table 3.

Table 3

| Sampling frequency<br>[kHz] | 12   | 8   | 6.4   | 5.3  | 4 |

|-----------------------------|------|-----|-------|------|---|

| Duration of SE<br>[s]       | 0.33 | 0.5 | 0.625 | 0.75 | 1 |

Sound Effects can be recorded by user similarly as messages, i.e. as any sound signals. They are used as sound indicators to indicate the status of the following functions:

- SE1: beginning of recording, forward and global erase.

- SE2: end of recording, individual erase or forward from last message.

- SE3: invalid erase operation.

- SE4: successful global erase.

Access to an individual SE is additionally signalled by LED1 blinking. This diode flashes once for SE1, twice for SE2 and so forth, and the blinking period depends on whether designated SE is programmed or not. If none of them are programmed the blinking periods are defined as  $T_{LS1}$ ,  $T_{LS2}$ ,  $T_{LS3}$  and  $T_{LS4}$  respectively. However, if these effects are programmed, during operation, LED1 flashes with periods  $T_{SE1}$ ,  $T_{SE2}$ ,  $T_{SE3}$  and  $T_{SE4}$  respectively and the related SE is played simultaneously. The blinking periods depend on the sampling frequency and are limited by the duration of the recorded SE. Related values of these parameters can be found in the ISD1700 series datasheet.

## 4.1.1. Entering SE mode

- Press and hold FWD button for minimum 3 seconds (FWD = L). LED1 will usually blink once and SE1 will be played simultaneously (if it is recorded). Only if playback pointer is at the last message or memory is empty, LED1 will blink twice and SE2 will be played simultaneously (if it is recorded).

- While holding FWD button, press and hold REC button (REC = L) until LED1 blinks once.

- Repeat flash of LED1 indicates that the device is in SE mode. SE1 is always the first effect to be accessible.

#### 4.1.2. SE editing

- After entering into editing mode, it is possible to perform record, playback and erase operation.

- Each pulsing (short pressing) of FWD button (short L-level pulse) causes an advance to the next SE and its edition. After forward operation, LED1 will blink 1 to 4 times to indicate which SE is active. If FWD button is pressed when SE4 is active, advance to SE1 occurs and LED1 blinks once to indicate that SE1 is active.

- To record the specific SE press and hold REC button. Recording continues as long as this button stays pressed.

For recording, either a signal from built-in microphone M1 or a signal from external source fed to P5 socket can be used.

- To playback the specific SE, pulse PLAY button (short L-level pulse). Pulse ERASE button to erase SE.

- While LED1 is blinking, the device ignores any input commands, thus one must wait until this diode stops blinking before starting any record, playback, erase and forward operation.

## 4.1.3. Exiting SE mode

Press and hold FWD button until the LED1 stops blinking and related SE is played (if recorded). Then press and hold REC button until LED1 blinks twice and the device will play SE2 (if recorded). At this moment, the device exits the SE mode.

#### 4.2. Record operation (REC)

This function, triggered by REC button or by L-level signal on P6/4, enables sequential recording of independent messages. Total recording duration depends on specific type of ISD1700. The source of recording can either be the built-in microphone M1 or external device connected to socket P5.

Press and hold REC button (REC=L). The device starts recording from memory row indicated by the record

pointer and continues recording until this button is released (REC=H) or until end of memory. When a record

cycle is completed, LED1 turns off and the record pointer moves to the next available row from the last recorded

message.

If the memory is full, next message recording will only be possible after erasing one of the existing messages. Also if power supply is interrupted during recording, the circular memory architecture will get faulted and the device disabled. Next time an operation is started, this abnormal state will be indicated by LED1 blinking seven times. The only way to recover the normal state is to perform global erase operation.

Recording operation is signalled by LED1, and moreover special effects SE1 and SE2 are associated with it, according to the principles below.

After pressing REC button:

- If SE1 is not programmed, LED1 turns on and remains on continuously.

- If SE1 is programmed, LED1 blinks and the device plays SE1 simultaneously (see point 4.1). Then record

operation begins and LED1 turns on. LED blinking period is determined by the recorded duration of SE1 (T<sub>SE1</sub>).

After releasing REC button or when memory is full:

- If SE2 is not programmed, LED1 switches off immediately to indicate end of recording.

- If SE2 is programmed, LED1 blinks and the device plays SE2 simultaneously (see point 4.1). Then LED1 switches off to indicate end of recording. LED blinking period is determined by the recorded duration of SE2 (T<sub>SE2</sub>).

Triggering of record operation during playback, erase or forward operation is an illegal action and is ignored.

#### 4.3. Playback operation (PLAY)

This function, triggered by PLAY button or by L-pulse (L-level signal) on P6/3, enables to playback sequentially recorded messages. There are two playback modes: edge-trigger mode and looping playback mode.

#### 4.3.1. Edge-triggered playback

- Pulsing (short pressing) PLAY button (short L-level pulse in PLAYE, active HL edge: PLAYE=HL) initiates

playback operation of the current message, i.e. the one which is indicated by the playback pointer. During

playback, LED1 blinks. Playback stops at end of message and the playback pointer returns to beginning of this

message.

- Re-pulsing PLAY button after completion of playback operation causes re-play of the same message from its beginning.

- Pulsing PLAY button again during playback immediately halts this operation and the playback pointer returns to beginning of this message.

For playback in this mode of current message only, duration of pulse L (pressing PLAY button) must be shorter than duration of the message. Otherwise, after playback of the current message, playback of the next message in memory commences and after its completion, the playback pointer shifts to the beginning of the second message. In this way, continuous playback is possible under specific conditions described later.

# 4.3.2. Looping playback

- Press and hold PLAY button (PLAYE =L). As long as this state is held, the device plays all messages sequentially (executing forward operations automatically) from the current message to its preceding message and then this cycle is repeated. During playback, LED1 blinks non-stop.

- If neither SE1 nor SE2 is programmed, after playback of the given message (except the last message in memory), LED1 blinks once with period T<sub>LS1</sub> due to forward operation. After the last message, LED1 blinks twice with the period T<sub>LS2</sub>.

- If both SE1 and SE2 are programmed, after playback of the given message (except the last message in memory), the device plays back SE1 and simultaneously LED1 blinks due to forward operation. Then the device continues to playback the next message and LED1 blinks. However, after playing back the last message, the device plays SE2 (due to forward operation) with LED1 blinking and then playback of the first message begins. Then this process is repeated.

Triggering of playback operation during record, erase or forward operation is an illegal action and is ignored.

# 4.4. Forward operation (FWD)

This function, triggered by FWD button or by L-pulse on P6/6, advances the playback pointer to beginning of the next message in forward direction. This enables finding any message among several recorded sequentially. It is only necessary to know the consecutive number of the message being searched for. This operation is executed in a circular way, i.e. when the playback pointer reaches the last message in memory, it will move back to the first message, etc.

- Pulse (short press) FWD button (active HL edge: FWD=HL). The playback pointer will move to beginning of the next message, which becomes the current message at the moment.

- If the device is in power-down state (no operation is in progress) and the playback pointer doesn't indicate the last message, then as a result of executing FWD operation:

- o the playback pointer will advance to beginning of the next message,

- $\circ~$  if SE1 is not recorded, LED1 blinks once for the period  $T_{\text{LS1}},$

- if SE1 is recorded, it is played and LED1 blinks once for the period determined by the recorded duration T<sub>SE1</sub> of this effect.

- If the device is in power-down state and the playback pointer indicates the last message, then as a result of executing FWD operation:

- o the playback pointer will advance to beginning of the first message,

- $\circ~$  if SE2 is not recorded, LED1 blinks twice for the period  $T_{\text{LS2}},$

- if SE2 is recorded, it is played and LED1 blinks twice for the period T<sub>LS2</sub> determined by the recorded duration T<sub>SE2</sub> of this effect.

- If the device is currently playing the message that is not the last one, then as a result of executing FWD

operation:

- o the playback halts,

- o the playback pointer advances to beginning of the next message,

- o if SE1 is not recorded, LED1 blinks once for the period T<sub>LS1</sub>,

- if SE1 is recorded, it is played and LED1 blinks once for the period T<sub>LS1</sub> determined by the recorded duration T<sub>SE1</sub> of this effect,

- o the message indicated by the pointer is played and LED1 blinks during this process.

- If the device is currently playing the last message, then as a result of executing FWD operation:

- o the playback halts,

- o the playback pointer advances to beginning of the first message,

- o if SE2 is not recorded, LED1 blinks twice for the period T<sub>LS2</sub>,

- o if SE2 is recorded, it is played and LED1 blinks twice for the period  $T_{LS2}$  determined by the recorded duration  $T_{SE2}$  of this effect.

- o the first message is played and LED1 blinks during this process.

Triggering of forward operation during record or erase operation is an illegal action and is ignored.

#### 4.5. Erase operation (ERASE)

This function, triggered by ERASE button or by L-pulse (L-level signal) on P6/5; it can be of two kinds: erasing individual messages or global erasing of whole memory.

#### 4.5.1. Individual erase

In this mode, it is possible to erase only the first or the last message and only if the playback pointer indicates one of them. Erasing individual messages other than the first or last message is not possible in standalone mode. Pulsing (short pressing) ERASE button (short L-level pulse in  $\overline{\text{ERASE}}$  signal, active HL edge:  $\overline{\text{ERASE}}$  =HL) causes the device to respond differently, depending on its actual status and current location of the playback pointer.

- If the device is in power-down state and the playback pointer indicates to the first (or last) message, then:

- o if SE2 is not recorded, LED1 blinks twice for the period T<sub>LS2</sub> and the first (or last) message is erased,

- if SE2 is recorded, it is played and LED1 blinks twice for the period T<sub>LS2</sub> and the first (or last) message is erased.

- the playback pointer moves to the new first message which previously was the second message (or to the new last message which previously was the last but one).

- If the device is in power-down state and the playback pointer indicates other than the first or last message, then:

- o if SE3 is not recorded, LED1 blinks three times for the period T<sub>LS3</sub> and no message is erased,

- o if SE3 is recorded, it is played back, LED1 blinks three times for the period T<sub>LS3</sub> and no message is erased,

- o the playback pointer remains in the same location.

- If the device is currently playing the first (or last) message, then:

- o the playback halts,

- the message is erased as scenario one described earlier.

- If the device is currently playing any message, other than the first or last, then:

- the playback halts,

- o procedures according to scenario two described earlier are realized.

Triggering of individual erase operation during a record or forward operation is an illegal action and is ignored. However, triggering of individual erase operation during playback will delete this message but only if it is the first or last message.

### 4.5.2. Global erase operation

This is a level-triggered function. Pressing ERASE button for about 2.5 seconds ( $\overline{\text{ERASE}} = L$ ) initiates global erase operation, and keeping this button in this state deletes all messages, except Sound Effects. The device responds differently, depending on its current state.

- If SEs are not programmed:

- if the current message is either the first or last one, after pressing ERASE button LED1 blinks twice for the period T<sub>LS2</sub> to indicate that the current message is being erased, however if the current message is other than the first or last one, LED1 blinks three times for the period T<sub>LS3</sub> to indicate that the current message is not erased,

- if ERASE button remains pressed for more than 2.5 seconds, LED1 blinks seven times to indicate that all messages are being erased,

- o if ERASE button is released (ERASE =H) before the first three blinks of LED1, the global erase operation will be cancelled otherwise the global erase operation will be performed up to the end.

#### If SEs are programmed:

- if the current message is either the first or last one, after pressing ERASE button the device plays SE2 and LED1 blinks twice for the period T<sub>LS2</sub> to indicate that the current message is being erased, however if the current message is other than the first or last one, SE3 is played and LED1 blinks three times for the period T<sub>LS3</sub> to indicate that the current message is not erased,

- o if ERASE button remains pressed more than 2.5 seconds, SE1 is played three times and LED1 blinks simultaneously this is a warning signal that after playing SE1 three times, global erase will be performed,

- if ERASE button is released before playback of the third SE1, global erase operation will be cancelled otherwise global erase will continue up to the end and after completion, SE4 will be played with LED1 flashing simultaneously.

It should be remembered that if power supply is interrupted during the erase operation, then (similarly as during recording) the circular memory architecture will be disturbed and the device will get disabled. Next time the device is switched on, this abnormal state will be indicated by LED1 blinking seven times. The only way to recover the proper state is to perform the global erase operation.

#### 4.6. Reset operation (RESET)

This function, triggered by RESET button (RESET =L) or by L-level signal on P6/8, performs global resetting of the device without erasing recorded messages. After its execution, the device enters into power-down mode and both the record and the playback pointers are moved to the last message.

#### 4.7. Volume operation (VOL)

This function, triggered by VOL button or by L-pulse on P6/1, performs circular change of volume on SP+/SP-and AUD/AUX outputs of ISD device (and thus on terminal strip P2). This is 8-step volume control and each step changes the volume by 4 dB. The default volume level, after power on or after reset operation, is the maximum level.

- Each pulsing of VOL button (active HL edge: VOL = HL) decreases the volume by one step until the minimum level is reached.

- After the minimum level is reached each pulsing of VOL button increases the volume by one step until the maximum level is reached and then this process is repeated.

## 4.8. Feed-Through operation (FT)

In standalone mode this function, triggered by FT button or by L-level signal on P6/2, configures the analog path as direct amplifier of the input sound signal from socket P5 to speaker and audio outputs.

- Pressing and holding FT button (FT =L) activates the feed-through mode which enables the sound signal from ANAIN input of ISD1700 (socket P5) to pass directly to both SP+/SP- and AUD/AUX outputs when the device is idle

- Activating FT function during record operation causes ANAIN signal (socket P5) to be recorded.

## 4.9. Voice alert function (vAlert)

This optional signalling function causes LED1 to blink slowly (every few seconds) after record operation to indicate presence of a new message while the device is in power-down state. Exit from the power-down state, by activating any operation, stops this signalling and restores the normal signalling mode.

ISD devices which have this function are marked as ISD1700...01.

# 5. SERIAL PERIPHERAL INTERFACE (SPI) MODE

ISD1700 circuits can also be controlled by 4-wire serial interface SPI whereby the system operates as "slave" device and "master" device is e.g. microcontroller. Realized in this mode are instructions that are equivalents of functions available in standalone mode (through pushbuttons). It also has the facility of addressing ISD internal sound memory to realize addressed record and playback. Access is also obtained to internal APC register (Chapter 3) enabling e.g. modification of internal links for audio signal (analog path configuration, irrespective of input signal for record and playback signal) and also activates or disables certain functions.

Data transmission protocol applied requires data from microcontroller shift registers of SPI is output by HL edge of SCLK signal. General principles of SPI transmission in ISD1700 circuits are described below:

- An SPI interface is initialized on HL edge of SS signal (P7/5 pin). This pin must be held on L-level during the entire data transmission process.

- Data is shifted into ISD1700 through MOSI line (P7/3 pin) on LH edge of SCLK clock signal (P7/4 pin), and shifted out through MISO line (P7/2 pin) on HL edge of SCLK signal, with LSB first.

- Data transmission into/from the device is performed by 7-byte opcodes, which contain commands, data and address bytes, depending on command type.

- While control and address data is shifted into the device through MOSI line, the status register and current row address are simultaneously shifted out through MISO line.

- Data transmission is completed on LH edge of SS signal.

- After completing SPI transmission, an interrupt signal is generated on INT /RDY output (P6/7 pin).

Table 4

| Decimal serial number           | Hex     | Binary        | Start time of an operation [s] for specific sampling frequency: |         |         |         |        |  |

|---------------------------------|---------|---------------|-----------------------------------------------------------------|---------|---------|---------|--------|--|

| of memory row                   | address | dress address |                                                                 | 8 kHz   | 6.4 kHz | 5.3 kHz | 4 kHz  |  |

| 17                              | 0x010   | 00000010000   | 0.000                                                           | 0.000   | 0.000   | 0.000   | 0.00   |  |

| 18                              | 0x011   | 00000010001   | 0.083                                                           | 0.125   | 0.156   | 0.188   | 0.25   |  |

| 19                              | 0x012   | 00000010010   | 0.166                                                           | 0.250   | 0.312   | 0.376   | 0.50   |  |

|                                 |         |               |                                                                 |         |         |         |        |  |

| 256 (the last row of ISD1730)   | 0x0FF   | 00011111111   | 19.908                                                          | 29.875  | 37.344  | 45.094  | 59.75  |  |

| 257                             | 0x100   | 00100000000   | 20.000                                                          | 30.000  | 37.500  | 45.283  | 60.00  |  |

|                                 |         |               |                                                                 |         |         |         |        |  |

| 336 (the last row of ISD1740)   | 0x14F   | 00101001111   | 26.573                                                          | 39.875  | 49.844  | 60.188  | 79.75  |  |

| 337                             | 0x150   | 00101010000   | 26.656                                                          | 40.000  | 50.000  | 60.377  | 80.00  |  |

|                                 |         |               |                                                                 |         |         |         |        |  |

| 416 (the last row of ISD1750)   | 0x19F   | 00110011111   | 33.237                                                          | 49.875  | 62.344  | 75.283  | 99.75  |  |

| 417                             | 0x1A0   | 00110100000   | 33.320                                                          | 50.000  | 62.500  | 75.471  | 100.00 |  |

|                                 |         |               |                                                                 |         |         |         |        |  |

| 496 (the last row of ISD1760)   | 0x1EF   | 00111101111   | 39.901                                                          | 59.875  | 74.844  | 90.377  | 119.75 |  |

| 497                             | 0x1F0   | 00111110000   | 39.984                                                          | 60.000  | 75.000  | 90.566  | 120.00 |  |

|                                 |         |               |                                                                 |         |         |         |        |  |

| 736 (the last row of ISD1790)   | 0x2DF   | 01011011111   | 59.893                                                          | 89.875  | 112.344 | 135.660 | 179.75 |  |

| 737                             | 0x2E0   | 01011100000   | 59.976                                                          | 90.000  | 112.500 | 135.849 | 180.00 |  |

|                                 |         |               |                                                                 |         |         |         |        |  |

| 976 (the last row of ISD17120)  | 0x3CF   | 01111001111   | 79.885                                                          | 119.875 | 149.844 | 180.943 | 239.75 |  |

| 977                             | 0x3D0   | 01111010000   | 79.968                                                          | 120.000 | 150.000 | 181.132 | 240.00 |  |

|                                 |         |               |                                                                 |         |         |         |        |  |

| 1216 (the last row of ISD17150) | 0x4BF   | 10010111111   | 99.877                                                          | 149.875 | 187.344 | 226.226 | 299.75 |  |

| 1217                            | 0x4C0   | 10011000000   | 99.960                                                          | 150.000 | 187.500 | 226.415 | 300.00 |  |

|                                 |         |               |                                                                 |         |         |         |        |  |

| 1456 (the last row of ISD17180) | 0x5AF   | 10110101111   | 119.869                                                         | 179.875 | 224.844 | 271.509 | 359.75 |  |

| 1457                            | 0x5B0   | 10110110000   | 119.952                                                         | 180.000 | 225.000 | 271.698 | 360.00 |  |

|                                 |         |               |                                                                 |         |         |         |        |  |

| 1696 (the last row of ISD17210) | 0x69F   | 11010011111   | 139.861                                                         | 209.875 | 262.344 | 316.792 | 419.75 |  |

| 1697                            | 0x6A0   | 11010100000   | 139.944                                                         | 210.000 | 262.500 | 316.981 | 420.00 |  |

|                                 |         |               |                                                                 |         |         |         |        |  |

| 1936 (the last row of ISD17240) | 0x78F   | 11110001111   | 159.853                                                         | 239.875 | 299.844 | 362.075 | 479.75 |  |

Memory is addressed in binary code with 11-bit address transferred via MOSI row according to the principles in Table 4. Binary digit 0 corresponds to logical L state and binary 1 to H. It should be remembered that the designated address always indicates memory row from which record or playback operation begins. Further internal addressing of consecutive memory cells is automatic through memory internal indicators. Addressing of messages starts from the 17th row, viz. from address 0x010 (binarily 00000010000) since the first 16 rows are reserved for sound effects recorded as described earlier.

Because of the built-in circular memory management protocol which controls message recording, it is necessary to comply with the following rules in SPI mode:

- arrangement of messages recorded in SPI mode using the address method, must match the circular memory structure,

- only one empty slot is allowed in the memory,

- it is necessary either before or after exiting SPI mode, to reset the device before any standalone operation is performed.

Failure to do the above actions may cause malfunctioning in standalone mode.

Details about SPI transmission protocol and relevant instructions performed by ISD1700 are beyond the capacity of this booklet. Full information regarding this matter is available in the manufacturer's documentation.

#### 6. BASIC TECHNICAL DATA OF MART1700 MODULE

- Supply voltage: +2.4 ... +5.5V, stabilized.

- Record duration depending on type of ISD1700: 30...240 s at 8 kHz sampling frequency.

- Non-volatile storage in ISD1700, 100-year message retention without supply.

- 100 000 record cycles.

- Control modes: by means of buttons or external signals (in standalone mode) or through SPI interface.

- Recording sound signal from built-in microphone or from external source.

- Input sound signal voltage on socket P5: max. 1 Vpp.

- Speaker output power (PWM type SP+ and SP- signals on terminal strip P3): 670 mW at 5.5 V supply voltage and 8 Ω speaker resistance.

- AUX analog signal voltage on output socket P4: max. 1 Vpp.

# 7. BIIL OF MATERIAL OF THE MODULE

| Symbol                     | Туре                             | Comments                                                           |

|----------------------------|----------------------------------|--------------------------------------------------------------------|

| Resistors (0.125 W):       |                                  |                                                                    |

| R1                         | $2.2~\mathrm{k}\Omega$           |                                                                    |

| R2, R3                     | $4.7~\mathrm{k}\Omega$           |                                                                    |

| R4                         | 53 k $Ω$                         |                                                                    |

| R5                         | 80 kΩ                            |                                                                    |

| R6                         | 100 k $\Omega$                   |                                                                    |

| R7                         | 120 k $\Omega$                   |                                                                    |

| R8                         | 160 k $\Omega$                   |                                                                    |

| R9, R13                    | $680~\Omega$                     |                                                                    |

| R10                        | $390~\Omega$                     |                                                                    |

| R11                        | 1 kΩ                             |                                                                    |

| R12                        | 10 kΩ                            |                                                                    |

| Capacitors:                |                                  |                                                                    |

| C1, C14                    | 4.7 μF/35V                       | electrolytic                                                       |

| C6, C8, C10, C12           | 100 μF/16V                       | electrolytic                                                       |

| C2, C3, C13                | 100 nF                           | MKT type film capacitor                                            |

| C5, C7, C9, C11, C15       | 100 nF                           | ceramic                                                            |

| C4                         | 220 nF                           | ceramic                                                            |

| C16                        | 1 μF                             | MKT type film capacitor                                            |

| <u>ICs:</u>                | ·                                |                                                                    |

| U1                         | ISD1700                          | any IC from this series                                            |

| <u>Transistors:</u>        |                                  |                                                                    |

| T1                         | BC337                            | h <sub>fe</sub> classification: 25                                 |

| Diodes:                    |                                  |                                                                    |

| D1, D2, D3, D4, D5, D6, D7 | 1N4148                           | switching diode                                                    |

| LED1                       | LTL4231NLC                       | green, low-current, 3 mm                                           |

| LED2                       | LTL4221NLC                       | red, low-current, 3 mm                                             |

| Other components:          |                                  |                                                                    |

| M1                         | CM-18W                           | electret microphone                                                |

| S1                         | DTS-61R                          | tact switch 6x6 mm, NO, dist. TME                                  |

|                            |                                  | ( www.tme.pl/index.phtml?lang=en )                                 |

| S2, S3, S4, S5, S6         | DTS-63K                          | tact switch 6x6 mm, NO, dist. TME                                  |

| S7                         | DTS-63R                          | tact switch 6x6 mm, NO, dist. TME                                  |

| P1                         | PC-GK2.1                         | DC power socket for PCB, 2.1/5.5 type, dist. TME                   |

| P2, P3                     | TB-3.8-P-2P-BL or TB-3.8-P-2P-GY | terminal strip 3.81 mm, 2-pin, dist. TME                           |

| P4                         | PHS-2B                           | chinch socket for PCB, dist. ELFA ( www.elfa.se )                  |

| P5                         | JC-128                           | jack stereo socket for PCB, dist. TME                              |

| P6                         | 22-27-2101                       | plug for PCB, straight, pitch 2.54 mm, 10-pin, dist. ELFA          |

| P7                         | 22-27-2051                       | plug for PCB, straight, pitch 2.54 mm, 5-pin, dist. ELFA           |

| J1, J2, J3, J4, J5, J6     | MX-90120-0122                    | pin header for PCB, male vertical, pitch 2.54 mm, 2-pin, dist. TME |

| J7                         | MX-90120-0123                    | pin header for PCB, male vertical, pitch 2.54 mm, 3-pin, dist. TME |

|                            |                                  |                                                                    |

Some of these components, mainly mechanical components (switches, sockets, headers), can be replaced with their equivalents of other firms.

## **CHANGES IN REV. 3:**

- 1. Revision of capacitor's value C1 = 4.7  $\mu$ F. 2. Revision of capacitor's value C4 = 220 nF.