# Nuvoton Audio Codec Motherboard

# **Evaluation Board User's Guide**

(For Nuvoton CODEC series: 8812, 8814, 8810, 88C10, 8811, 8820, 8822, 8822L, 88C22, 8401, 8402, 8501, and 8502.)

#### Introduction

This system is a combination of hardware and software that enables fast and detailed evaluation of Nuvoton audio products. The hardware consists of a base evaluation board and a daughter card which contains the specific audio product to be evaluated. The daughter card system enables the use of the same base motherboard hardware and software to evaluate many different Nuvoton audio products. The software must be installed on a Windows based PC, and is compatible with most PC products and versions of the Windows operating system.

#### Summary Hardware Description

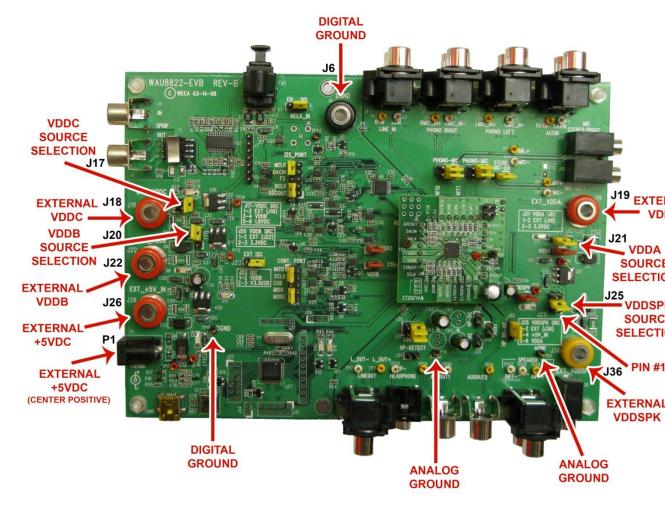

The motherboard includes a wide range of audio, power, and data input/output connectors that enable testing a very wide range of features and audio products. The motherboard kit includes a USB cable and the specific daughter card that was ordered with the system.

In most applications, the motherboard can be entirely powered via the included USB cable, and most testing can be done using only this cable as the power source. This system uses a large amount of USB power, and should NOT be used with longer or unknown quality USB cables. These can cause unreliable operation.

If additional daughter cards have been ordered with this system, it is strongly recommended to first install the software and test the system using the pre-installed daughter card. The motherboard and pre-installed daughter card have been carefully tested together, and it is best to fully verify the hardware/software system is working before changing to a different daughter card.

#### **Summary Software Description**

The supporting software includes many features that enable quick and thorough evaluation of the various supported Nuvoton audio products. The software includes easy-to-use predefined configurations, an intuitive GUI user interface, and also detailed register and bit manipulation controls to facilitate every technical level of device operation and evaluation.

Depending on how this system was ordered and delivered, software may either be provided on an included CD-ROM, or may be separately downloaded via the Internet. The software must be installed on a Windows based PC system. Downloaded versions of the software will require a Username and Password in order to start the installation process. Normally, this login information will have been provided in advance by a Nuvoton sales representative.

#### TABLE OF CONTENTS

| 1. | Hardware | e Overview                                          | 6   |

|----|----------|-----------------------------------------------------|-----|

| 2. | Software | Installation and Set-Up                             | 7   |

| 3. | PC Confi | guration                                            | 8   |

| 4. |          | the GUI Application                                 |     |

| 5. | 0        | started Using the GUI Application                   |     |

| -  |          | IO Panel Status Indicators                          |     |

| 0. | 5.1.1.   | Device Attached/Detached Indicator                  |     |

|    | 5.1.2.   | Power Up Indicator                                  |     |

|    | 5.1.3.   | Busy Indicator                                      |     |

| Б  |          | oduction to Main Menu Bar                           |     |

| 5. |          |                                                     |     |

|    | 5.2.1.   | Device                                              |     |

|    | 5.2.2.   | Mode                                                |     |

| _  | 5.2.3.   | Config                                              |     |

| 6. |          | rol Tabs                                            |     |

| 6. |          | no Panel                                            |     |

|    | 6.1.1.   | Step 1: Configure                                   |     |

|    | 6.1.2.   | Step 2: Load Settings                               | .13 |

|    | 6.1.3.   | Step 3: Evaluate                                    | .13 |

|    | 6.1.4.   | Demo Example for NAU8822                            | .14 |

| 6. | 2. Path  | Niew Control Panel                                  | .14 |

|    | 6.2.1.   | Description of Special Icons in Path View           |     |

|    | 6.2.2.   | Path View Navigation Shortcuts                      |     |

| 6. | 3. Devi  | ice Control Panel                                   |     |

| -  | 6.3.1.   | Device Settings                                     |     |

|    | 6.3.2.   | Board Settings                                      |     |

|    |          | . Command Interface                                 |     |

|    |          | 2.1.1. External Control                             |     |

|    |          | 2. 12S Signal Connection                            |     |

|    |          | 2.2.1. Digital Audio Reset                          |     |

|    |          | •                                                   |     |

|    |          | 2.2.2. I2S Master                                   |     |

|    |          | 3.2.2.2.1. On-Board USB                             |     |

|    |          | 3.2.2.2.2. Audio Precision I2S Master               |     |

|    |          | 3.2.2.2.3. Digital Audio Master                     |     |

|    |          | 2.2.3. I2S Slave                                    |     |

|    |          | 3.2.2.3.1. Audio Precision Slave Mode               |     |

|    |          | 3.2.2.3.2. Digital Audio Slave                      |     |

|    |          | 2.2.4. Direct Digital Audio Interface Header Enable |     |

|    | 6.3.3.   | Power Management                                    |     |

| 6. | 4. Inpu  | t Path Control Panel                                | .23 |

|    | 6.4.1.   | Microphone Bias                                     |     |

| 6. | 5. ADC   | C/Filtering Control Panel                           | .24 |

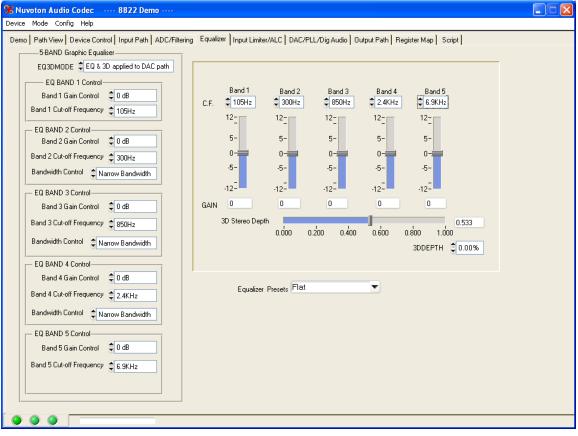

| 6. |          | alizer Control Panel                                |     |

| 6. |          | t Limiter and ALC Control Panel                     |     |

| 6. |          | C/PLL/Digital Audio Control Panel                   |     |

| 5. |          |                                                     |     |

|    | 6.8.1.   | DAC Control                                         | .28 |

|    |          | . Oversampling                                      |     |

|    | 6.8.2.   | PLL Control                                         |     |

|    | 0.0.2.   |                                                     | .20 |

| 6.8.2.1. REFIMP                                      | 29 |

|------------------------------------------------------|----|

| 6.8.2.2. FS (Frame Sync)                             |    |

| 6.8.2.3. Clock Prescalers                            | 30 |

| 6.8.2.4. Config PLL                                  | 30 |

| 6.8.3. Digital Audio Control                         |    |

| 6.8.3.1. Clock Generation Control                    | 31 |

| 6.8.3.1.1. CLKIOEN Master Mode                       | 31 |

| 6.8.3.1.2. CLKM Master Clock                         | 32 |

| 6.8.3.1.3. BCLKSEL                                   | 32 |

| 6.8.3.1.4. SMPLR Sample Rate                         | 32 |

| 6.8.3.2. Companding Control                          | 32 |

| 6.8.3.2.1. PASSTHRU                                  |    |

| 6.8.3.3. Audio Interface Control                     |    |

| 6.8.3.4. Jack Detect Bus Switching                   | 32 |

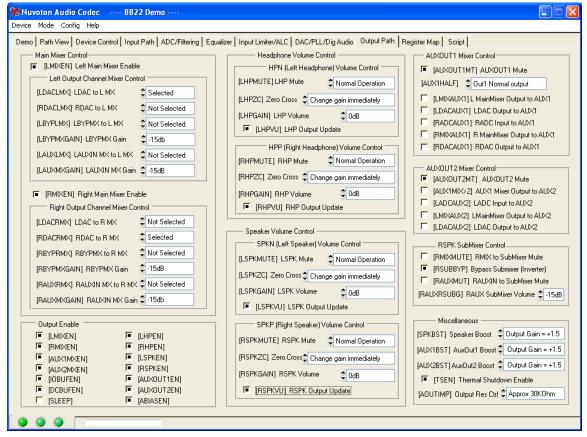

| 6.9. Output Path Control Panel                       | 33 |

| 6.10. Register Map Control Panel                     | 34 |

| 6.10.1. Register Map Bit Control                     |    |

| 6.10.1.1. Register Map Update Bits (write-only bits) | 35 |

| 6.10.2. Audio Codec Register Control                 | 35 |

| 6.11. Script Control Panel                           |    |

| 6.11.1. Script Panel Structure                       |    |

| 6.11.2. Script Panel Syntax                          | 36 |

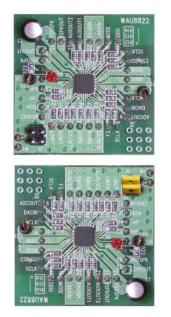

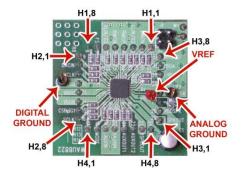

| 7. Daughter Card System                              |    |

| 7.1. Changing Daughter Cards                         |    |

| 7.2. NAU8822 Daughter Card                           | 38 |

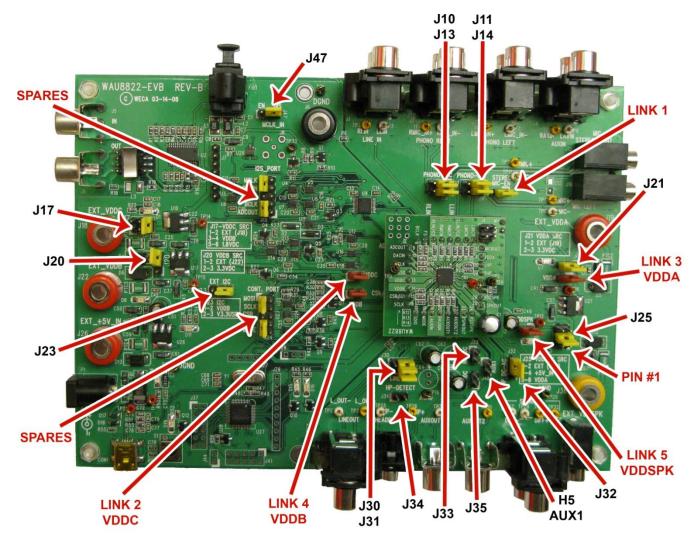

| 8. Jumpers and Connectors                            |    |

| 8.1. Power Related Connectors and Options            |    |

| 8.1.1. Summary of Power Options and Limits           |    |

| 8.1.2. Main 5Vdc Power                               |    |

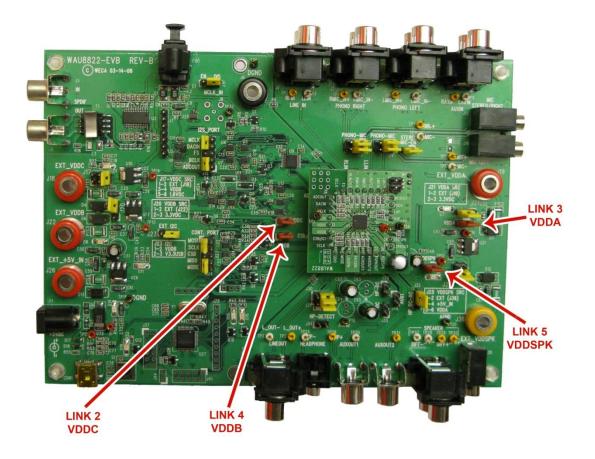

| 8.1.3. Power LINK Jumpers                            |    |

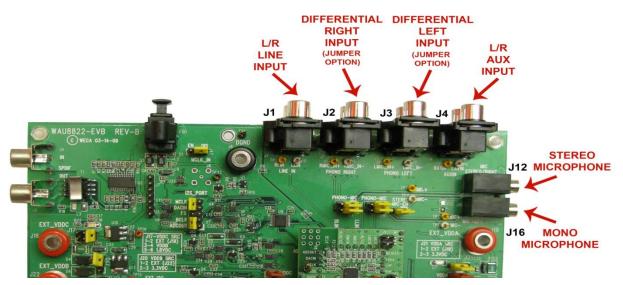

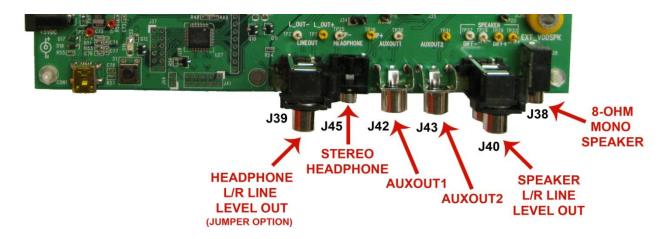

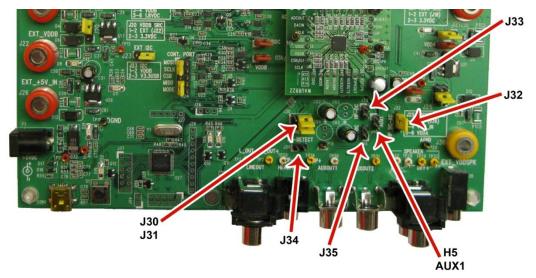

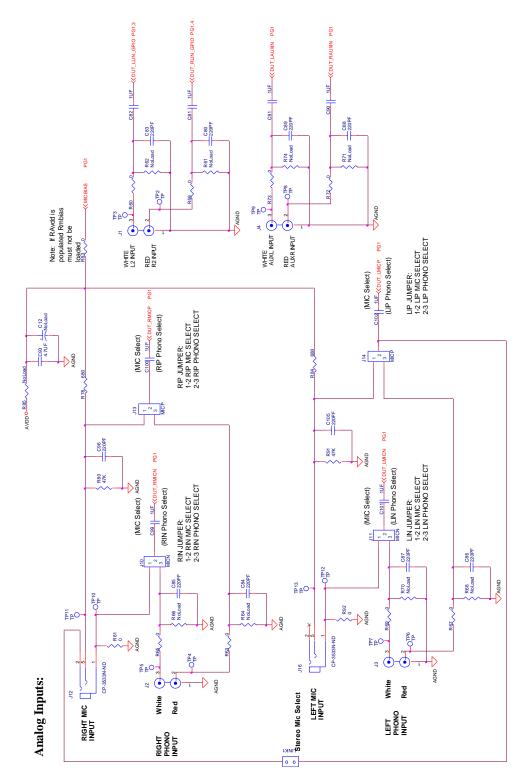

| 8.2. Analog Inputs for NAU8822                       |    |

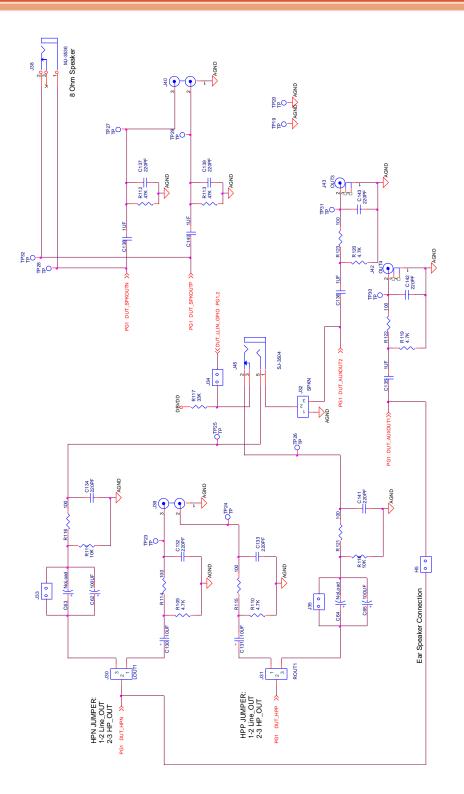

| 8.3. Analog Outputs for NAU8822                      |    |

| 8.3.1. Analog Output Options for NAU8822             |    |

| 8.3.1.1. Headphone Detect                            |    |

| 8.3.1.2. Headphone Virtual Ground                    |    |

| 8.3.1.3. DC Coupled Headphone Outputs                |    |

| 8.3.1.4. Ear Speaker Mode                            | 46 |

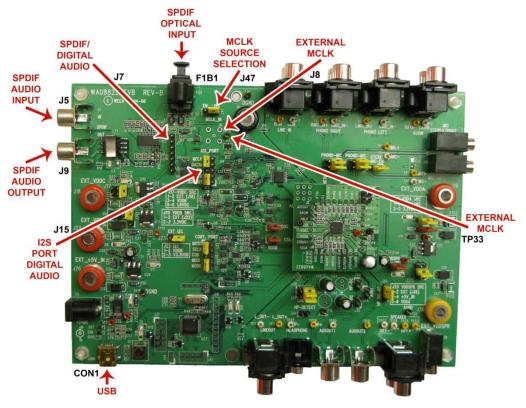

| 8.4. Digital Audio Using the NAU8822               | 47 |

|----------------------------------------------------|----|

| 8.4.1. NAU8822 Master Clock Requirement            | 47 |

| 8.4.2. Master Clock Selection                      |    |

| 8.4.3. Frame Sync (Sample Rate Clock)              | 47 |

| 8.4.4. Bit Clock (BLCK)                            | 47 |

| 8.5. Digital Audio Input                           |    |

| 8.5.1. Formatted Digital Audio                     |    |

| 8.5.2. USB Audio                                   |    |

| 8.5.3. Unformatted Audio                           | 49 |

| 8.6. Digital Audio Output                          | 50 |

| 8.6.1. Formatted Digital Audio                     | 50 |

| 8.6.2. USB Audio                                   | 50 |

| 8.6.3. Unformatted Audio                           | 50 |

| 8.7. Digital Audio Related Connector Options       | 51 |

| 8.8. USB and External Control CONNECTIONS          | 52 |

| 8.8.1. Special Connectors                          | 52 |

| 8.9. Jumpers                                       | 53 |

| 8.10. Table of Jumper Options                      |    |

| 8.11. Test Points                                  | 55 |

| 8.12. Table of Test Points                         |    |

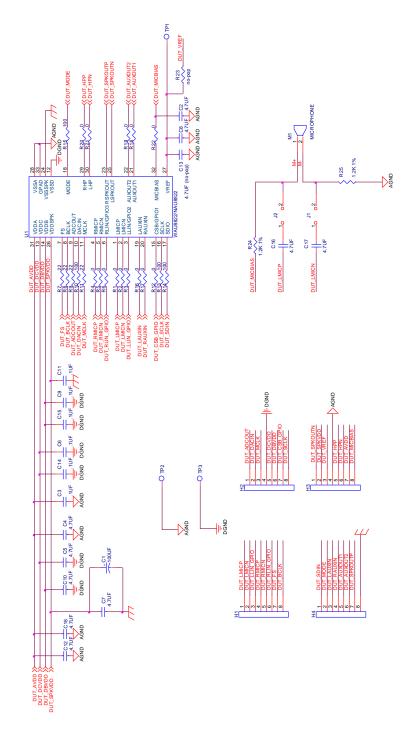

| 9. NAU8822-EVB Schematics (High Resolution Images) | 57 |

| 10. LIST OF FIGURES                                |    |

| 11. LIST OF TABLES                                 | 65 |

| 12. VERSION HISTORY                                | 65 |

|                                                    |    |

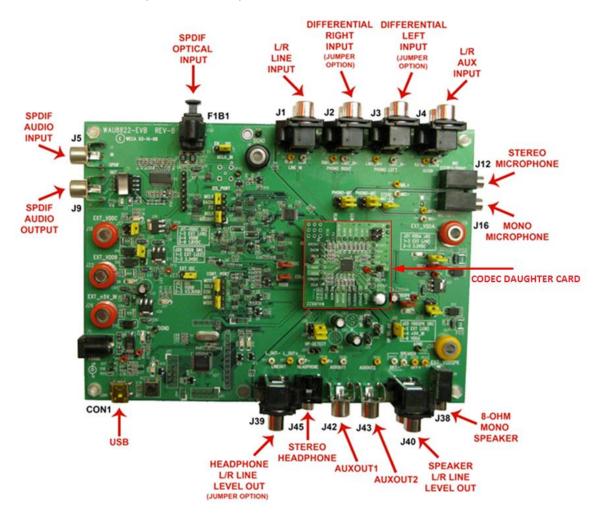

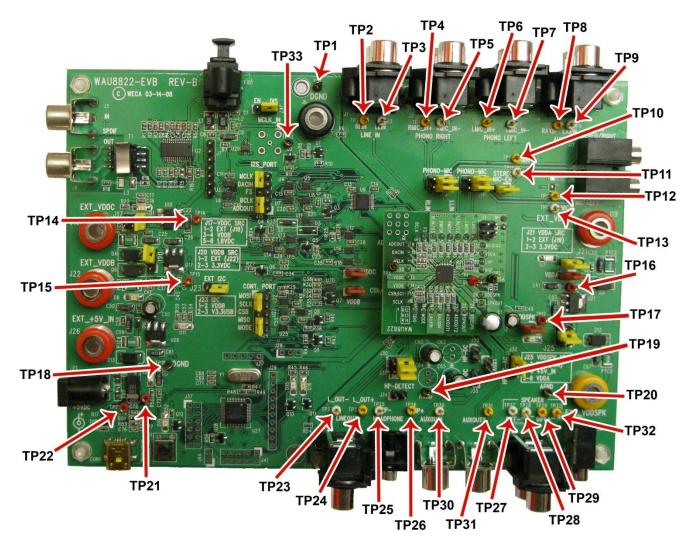

## **1** Hardware Overview

All instructions in this guide require some familiarity with the physical layout of the motherboard and daughter cards. This information is introduced as needed, so it is not necessary at first to memorize or understand the complete layout and functions of the hardware.

There are various daughter card can be used for the same motherboard. They are NAU8812, NAU8814, NAU8810, NAU88C10, NAU8811, NAU8820, WAU8822, NAU8822L, NAU88C22, NAU8401, NAU8402, NAU8501, and NAU8502.

However, to get started, a few basic inputs and outputs must be noted. The USB connector and external audio inputs/outputs are highlighted in this section.

Control and power are supplied via the USB connector. When first learning how to use this system, it is recommended to choose a simple audio input and output combination. One example would be to input audio from a line level source such as a CD-audio player into the Aux inputs, and to listen to the output on the headphone connector.

Figure 1: CODEC Motherboard SYSTEM

## 2 Software Installation and Set-Up

The software is installed using a standard PC installation software program that has been downloaded or supplied on a CD-ROM. The software installer is not an auto-start program, so it is necessary to locate the single executable (type .exe) file and run this program manually.

If the installation software has been downloaded, the installer program will request a Username and Password to complete the installation procedure. Normally, these will have been provided in advance by a Nuvoton sales representative. Using a downloaded version of the software will insure having the most recently released version of the program.

If no version of this GUI Application has been previously installed on the PC, components will be added that enable the PC to recognize the Nuvoton USB audio hardware. Depending on the operating system and configuration, it may be necessary to reboot the PC after the first-time installation. If the installation program recommends rebooting the PC, it is best to do so. However, a requested reboot can usually be ignored, and all components will operate correctly.

The software installation procedure does not overwrite or replace older versions of the GUI Application software. In some cases, it may be desirable to keep older versions of the application available while learning to use a newer version.

If it is preferred to remove older versions of the application, the software should be removed BEFORE installing the new software. The reason is that the un-install process may remove common shared library components needed by the newer version of the application. An undesired version application can be removed (before installing a newer version) using the standard un-install feature included in Windows PC "Add or Remove Programs" control panel.

## **3 PC Configuration**

IMPORTANT INFORMATION: The GUI Application software installation and configuration is entirely automatic. However, because the EVB is registered with the PC as an "Audio Device," sound from inside the PC may automatically be routed to the Nuvoton EVB. The EVB is registered as a USB audio device, because it has the capability to receive an audio stream over the USB bus.

Thus, after plugging the EVB into a PC, audio inside the PC may appear to stop working or be changed in ways that are surprising. Managing the PC audio routing will be especially important if it is desired to use the PC as an audio source as part of the EVB evaluation process.

Therefore, it is important to understand how to manage and control the PC built-in software and hardware audio features. What happens automatically, and the details of how to manage audio inside the PC will vary depending on the Windows version and specific PC hardware. Further details may be different if other audio hardware and or software has been installed on the PC.

In all Windows systems, the management of audio is similar. This is typically done using the "Control Panel" option in the Start Menu, and then selecting the appropriate audio control icon or menu item. It may also be possible to access the PC audio control panel by clicking or rightclicking on the speaker icon in the Task Bar, normally at the bottom of the PC screen.

After activating the audio control panel, there will be various options. There will be an option for routing sound to and from the PC, and in this option there will be a list of possible audio devices. The Nuvoton EVB is registered as an "Audio Device." It is possible other audio devices attached to the PC may have the same or similar name. The Nuvoton EVB can be identified in this case by unplugging/replugging into the PC to see which item is changed in the list of audio devices.

Again depending on the Windows system and configuration, any selection made in the control panel may later be automatically changed by the PC system. Also, media player software may not immediately recognize that the PC audio path has been changed. It is best to quit and then restart any media player application after making a change to the audio routing using the PC control panel.

## 4 Running the GUI Application

After installation, and depending on the Windows operating system and installation options, an icon to start the application may have been added to either or both the Desktop and Start Menu locations. The program will always be available under the Run option in the Start Menu. The application name will always start with the word "Nuvoton."

The application may be started with or without the motherboard USB hardware attached. If the motherboard is not attached, the application will run in a "software demo" mode that enables becoming more familiar with the software.

After starting, the following start-up screen will be displayed.

The normal use of the application at this time is to click on the icon that matches the actual device that is on the installed hardware daughter card. Clicking on this icon will then configure the software to match the attached hardware, and after this, evaluation can begin immediately. The next window that opens will be the DEMO page that is explained below.

Figure 2: GUI APPLICATION START-UP SCREEN

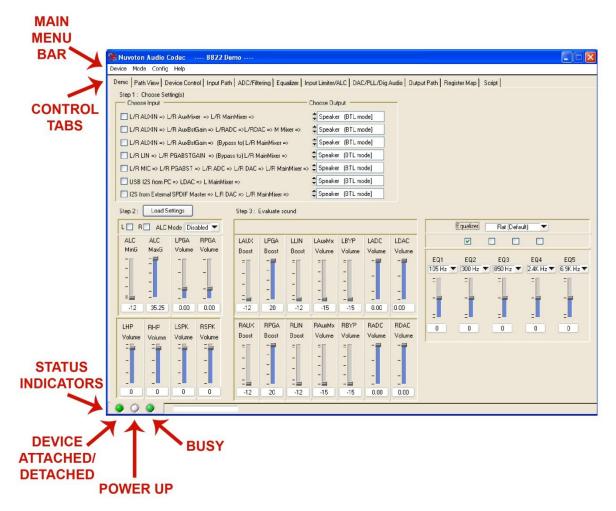

## **5** Getting Started Using the GUI Application

After making the selection on the start-up screen to select the audio device to be evaluated, the GUI Application will open to the Demo Panel screen. All panels are structured similarly and include the Main Menu Bar, Control Tabs, and Status Indicators.

### 5.1 DEMO Panel Status Indicators

The Status Indicators are located in the lower left hand corner of every Control Tab screen. These indicators are especially important, as they provide the highest level of system status.

#### 5.1.1 Device Attached/Detached Indicator

The Status Indicator on the far left is the most important. This indicator will be Green when the motherboard hardware is attached to the PC, and signals that the PC has recognized the hardware and established communication with the hardware. If the indicator is white, then no interaction with the motherboard or daughter card is possible.

#### 5.1.2 Power Up Indicator

The middle status indicator is the Power Up Indicator. This will be Green after the software has powered up all elements on the motherboard necessary to interoperate with the daughter card. If the indicator is white, then the motherboard and communications between the motherboard and daughter card have not been set up, and no interaction with the daughter card is possible.

#### 5.1.3 Busy Indicator

The status indicator on the right-hand side indicates when the GUI Application is making changes to the motherboard and/or the daughter card. This will be Green when all changes are completed and the hardware is configured for operation. This indicator will be white when the GUI Application is busy making changes to the motherboard and/or the daughter card.

#### 5.2 Introduction to Main Menu Bar

The Main Menu Bar is included on the Demo Panel, the start-up screen, and all other views. This enables direct and quick access to some features common to all devices. Many of these features are for more experienced users, and this section can be studied as needed at a future time.

#### 5.2.1 Device

The Device menu allows changing the selected daughter card device without restarting the application. This can be useful if the wrong device was accidentally selected, or it can be used to switch daughter cards without restarting or powering down the hardware. However it is preferred to power-down the hardware and restart the application to change daughter cards This more conservative procedure will insure the greatest reliability for both the hardware and software.

#### 5.2.2 Mode

The Mode selection is normally automatic and the user should NOT change this. This menu item enables changing the hardware control bus protocol between the motherboard and the audio device being tested.

The Mode feature is included for instances when the motherboard or daughter card hardware has been custom modified to be hard-wired into a particular control bus configuration. Then, it is important to have a top-level menu control to change this selection. The control bus modes are explained in more detail in the section describing the Device Control menu tab functionality.

#### 5.2.3 Config

The Config menu enables Exporting or Importing settings from a standard file stored on the PC system. This feature saves only the settings for the audio device being tested, and not the configuration of the motherboard itself. So, the motherboard must already be initialized and set up in the desired mode before executing the Import function.

Export/Import is useful for saving configurations for future use, or for sharing configurations with other users. It is also a convenient way to copy/paste a set of desired register settings from the EVB environment directly into software used to control the device in the actual end product.

# nuvoTon

## 6 The Control Tabs

All of the main features and many options are selected by choosing one of the Control Tabs. This is the horizontal menu list immediately below the Main Menu. After the user selects the device, the application automatically opens into the Control Tab for the Demo Panel. It is best to first work with the Demo Panel to begin learning how to use this application and the other Control Tabs. The following sections describe the functions of each Control Tab in more detail.

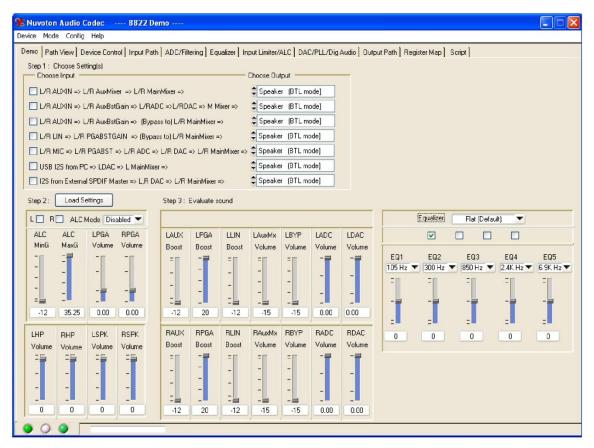

#### 6.1 Demo Panel

The Demo Panel is important, because it enables complete, proven, and working examples of how to configure the device on the daughter card. This panel also will automatically initialize the EVB (if necessary) and do other initialization as may be needed to start up the device on the daughter card. The idea of this panel is to be able to use the EVB with almost no understanding of any other function of the EVB and its many options.

The Demo Panel breaks down operation of the EVB into three simple steps. These are grouped together visually on the PC screen, and each group is labeled as a numbered Step.

Figure 4: DEMO CONTROL PANEL

#### 6.1.1 Step 1: Choose Settings

The Choose Settings selection enables selection of the input, as well as the entire path for audio from the selected input, through all of the device options, and then to the output. The path descriptions are listed in an abbreviated form to fit within the GUI display.

The Choose Settings selection also enables choosing various possible outputs and output combinations that will work with the selected input. These selections may be scrolled one-at-a-time using the up/down arrows in the output selection area. They may also be selected directly by clicking on the text of the output path that is shown. This will open a pop up a window showing all of the possible output selections, and then the desired selection can be made directly.

#### 6.1.2 Step 2: Load Settings

Clicking on this button will cause all of the desired settings to be loaded into the audio device being tested. Additionally, any necessary changes to the EVB initialization or configuration will be performed automatically at this time.

While the settings are being loaded, the Status Indicators at the bottom left of the screen may change from Green to White. IMPORTANT: If the configuration was successfully completed, all three Status Indicators will be Green, and the configuration is now ready for evaluation.

#### 6.1.3 Step 3: Evaluate Sound

The bottom portion of the screen includes a few controls that enable experimentation with some of the settings that can be changed on the audio device being tested. These can be changed using the GUI, and the effect on the device will be immediate. Do NOT push the "Load Settings" button again while using this feature. This will cause all of the settings to revert to the original selected Demo configuration.

At this time, it may be useful to select any of the other Control Tabs. These make available many more controls and features that can be changed after the Demo selection has been loaded.

## 7 Demo Example for NAU8822

In this example, the goal is to pass audio from the left and right auxiliary inputs, into the ADC, from the ADC into the DAC, and then output to the headphones. This is accomplished by the following three steps:

Choose: "L/R AUXIN => L/R AuxBstGain => L/RADC => L/RDAC => M Mixer => Select for the output: Headphone Push the "Load Settings" button and verify all three Status Indicators change to Green

At this point, any line level audio input attached to the Aux inputs should be audible in a headphone attached to the headphone jack. A suitable line level audio source would be the output from a CD-audio player or other media player device.

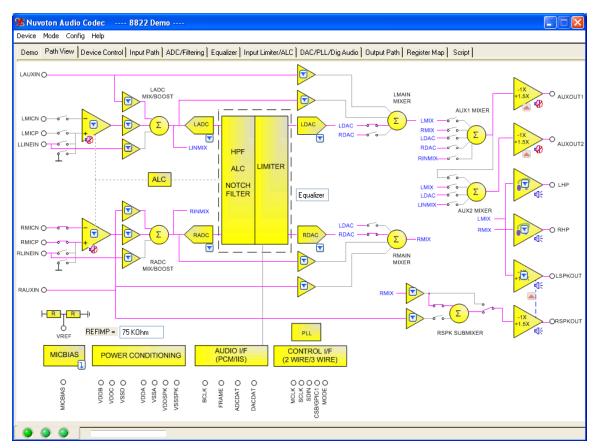

#### 7.1 Path View Control Panel

This panel shows in a graphical form the internal structure of the device being tested as it related to the available input, output, and control pins on the device. This is a highly interactive panel, and most of the features and controls are "clickable." This means that on the GUI screen you can simply click on a functional block or path and change its settings. You can also use this panel to see some of the settings that are currently in use.

Figure 5: PATH VIEW

This panel is intended to be used after a full set of settings has already been loaded into the device. This panel is difficult or impossible to use without having done this first. The main reason for this is that power control features are in the "off" condition, and these are not all directly available on the Path View.

To simplify use of the Path View, the Demo settings have been set up with all of the power control features in the "on" condition. This makes the Path View simpler to use, because it may not be at all obvious that a particular path is not working because one of the elements in the path does not have power.

#### 7.1.1 Description of Special Icons in Path View

Here is a summary of the "language" that can be used in this graphical environment:

The active path over which audio is enabled, is indicated by red colored lines in the GUI. In some cases, the lines are clickable and the path can be enabled/disabled simply by clicking on the line. This includes on/off switches which are also clickable with the active path indicated in red.

A speaker icon indicates that an output or input block is enabled. The disabled state will show the speaker icon with the international red "crossed out" overlay.

Items for which a drop-down or pop-up menu will appear are marked with a small down-arrow icon. This can be used to either view the current setting or to change a setting.

On NAU8822 devices, some of the outputs can be in a "boost" or "non-boost" gain configuration. This status is indicated near the output icon with a red up-arrow symbol to indicate the Boost state, or a red horizontal line symbol indicating the "Non-Boost" state.

Additionally, if a block is does not have power, this will be indicated by a right-angle down-arrow icon. To reduce visual clutter on the display, the "power-on" status is not shown. Because the Demo selections enable all power to all blocks, no power-down icons will normally be seen. However, if power is turned off using other Control Tabs, or the Path View is selected before loading any settings into the device, then the power-down icons will be visible.

#### 7.1.2 Path View Navigation Shortcuts

Clicking on blocks in the GUI view that have many functions will in some cases cause the display to switch to the Control Tab view appropriate for that block. This is a quick, powerful, and convenient way to change features in a block too complex to show in this Path View.

After clicking on a block that switches to a different Control Tab view, changes can be made in that view. When the changes are complete, simply right-click on the current Control Tab view, and the display will automatically switch back to the Path View. The Path View will automatically be updated to show any changes that were made in any of the other Control Tab panels.

#### 7.2 Device Control Panel

This panel modifies the basic configuration of both the motherboard and the audio device under test. In general, these features are for advanced users. Except for the "Initialize Board," "Initialize Device," and "Device Control" radio buttons, other settings in this panel should not be changed without a good understanding of the underlying functions.

The panel manages four basic groups of functions:

- 1) Radio button controls for motherboard and device management

- 2) Board Settings to select various motherboard hardware configuration options

- 3) Device Settings to select power options for high voltage NAU8822 outputs

- 4) Power Management features for the NAU8822 device

For less experienced users, the only Device Control radio buttons that should be used are the "Initialize Board" and "Initialize Device" buttons. These set up the motherboard and device, respectively, to basic starting conditions. These buttons may be most useful after having made many changes, and the state of the motherboard or device is unclear.

| 🛞 Nuvoton Audio Codec 📖 8822 Demo 📖 🔲 🗌 🔤 🔀                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Device Mode Config Help                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| Device       Mode       Config       Help         Demc       Path View       Device Control       Input Path       ADC/Filtering       Equalizer       Input Limiter/ALC       DAC/PLL/Dig Audio       Output Path       Registe         Initialize Board       Initialize Device       Initialize Device       Device Settings       Device Settings         Command Interface       Speaker Power Supply       VDDSPK = 5V       (Output Boost = 1.5k)       VDDSPK = 5V       (Output Boost = -1.0)         VDDSPK = Read/Write       I2C CLK       500K       Device Control       Device Control         External Control       Set Mode Pin High       Power Up       Reset Device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | r Map   Script  <br>Power Management<br>[ [DCBUFEN]<br>[ [AUX1MXEN]<br>[ [AUX1MXEN]<br>[ [AUX2MXEN]<br>[ [AUX2MXEN]<br>[ [PLLEN]<br>[ [MICDIASEN] Microphone Bias Enable<br>[ [ABASEN]<br>[ [IOBUFEN]<br>[ REFIMP] 75 KDhm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| □ Digital Audio Reset         □ Digital Audio Reset         □ Digital Audio (125) Mode [Feed MCLK to device]         □ Audio Precision (125) Master Mode Interface Enable         □ Digital Audio (125) Master Mode Interface Enable         □ Digital Audio (125) Slave Mode Interface Enable         □ Digital Audio (125) Interface Header Enable         □ Digital Audio (125) Inter | IHHEN     IHHEN     IHHEN     IHHEN     ILHFEN     ILLFEN     ISLEEP     IGSTEN     RADC Mix/Boost stage Enable     ILBSTEN     LADC Mix/Boost stage Enable     ILBSTEN     ILADC Mix/Boost stage Enable     ILFGAEN     ILLFACEN     ILFT     ILFT     ILLFACEN     ILLFACEN |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | [LDACEN] Lett Channel DAC Enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

Figure 6: DEVICE CONTROL OVERVIEW

#### 7.2.1 Device Settings

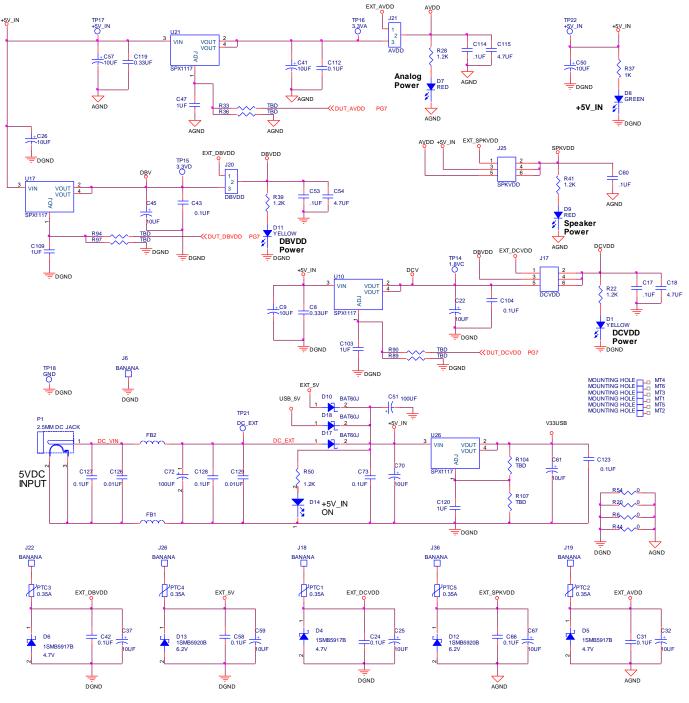

This changes the 5-volt or 3-volt settings of the NAU8822 outputs to match the actual voltage supplied on the VDDSPK pin. Management of the power options is explained in other sections of this document.

IMPORTANT: These settings should NOT be changed unless work is being done to change the internal or external VDDSPK voltage. For reliable operation, it is very important that these settings match the actual voltage on VDDSPK. The motherboard is set up by default to the 5-volt settings for VDDSPK, and this default software selection matches this default configuration.

The other Device Control radio buttons change various features as indicated by the text in the button. These change many different register values, and in many cases require a detailed understanding of information in the device data sheet and/or design guide.

- Reset: Writes to Register 0x00 of an NAU8822 device for its Reset condition

- PowerUp: Turns on basic registers to put an NAU8822 device into an "on" condition

- PowerDown: Sets an NAU8822 device into a low power "sleep" condition

- MuteAllOutputs: Enables only the Mute function on NAU8822 outputs

- EnableAllOutputs: Turns on power control bits for all outputs

- DisableAllOutputs: Turns off power control bits for all outputs

- LoadDefaultUpdateBits: Write to update bits to cause update feature to take place

Figure 7: DEVICE CONTROL PANEL - DEVICE SETTINGS

#### 7.2.2 Board Settings

These settings change the basic configuration of the motherboard communications with the device on the daughter card. These can affect the control bus mode, the I2S audio data stream, and also select external connectors as alternative sources and sinks for these signals.

IMPORTANT: Changes to this portion of the panel do NOT become effective until pushing the "Config Board" radio button. This button is located at the bottom of this grouping of controls.

| 🕦 Nuvoton Audio Codec 📖 8822 Demo 📖 🔲 🗌 🔀                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                            |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Device Made Config Help                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                            |  |

| Device Mode Config Help<br>Demo Path View Device Control Input Path ADC/Filtering Equalize<br>Initialize Board<br>Board Settings<br>Command Interface<br>3 Wire SPI Mode - Write Only (4 Wire SPI when reading)<br>4 Wire SPI Mode - Read/Write<br>12C Mode - Read/Write<br>12C CLK 500K ▼<br>External Control Set Mode Pin High                                                                                                                                                                   | Initialize Davice Device Settings Speaker Power Supply VDDSPK = 5V (Output boost = 1.5x) VDDSPK = 3.3V (Output Boost = -1.0) Device Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ster Map   Script  <br>Power Management<br>[ [DCBUFEN]<br>[ [AUX1MXEN]<br>[ [AUX2MXEN]<br>[ [PLLEN]<br>[ [MICBIASEN] Microphone Bias Enable<br>[ [ABIASEN]<br>[ [BEJFEN]<br>[ [BEFIMP] ] 75 KOhm                                                                                                                           |  |

| I2S Signal Connection         Digital Audio Reset         I2S Master         Øn-Board USB (I2S) Mode [Feed MCLK to device]         Audio Precision (I2S) Master Mode Interface Enable         Digital Audio (I2S) Master Mode Interface Enable         I2S Slave         Audio Precision (I2S) Slave Mode Interface Enable         Digital Audio (I2S) Slave Mode Interface Enable         Digital Audio (I2S) Slave Mode Interface Enable         Digital Audio (I2S) Slave Mode Interface Enable | Power Up Reset Device Power Down Mute All Outputs Load Default Update Bits Enable All Outputs Disable All Outputs Power Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | [RHPEN]     [LHPEN]     [LHPEN]     [SLEEP]     [RBSTEN] R ADC Mix/Boost stage Enable     [LBSTEN] L ADC Mix/Boost stage Enable     [RPGAEN] Right Channel PGA Enable     [LPGAEN] Lett Channel PGA Enable     [RADCEN] Right Channel ADC Enable     [LADCEN] Lett Channel ADC Enable     [LADCEN] Lett Channel ADC Enable |  |

| Direct Digital Audio ((25) Interface Header Enable<br>Config Board                                                                                                                                                                                                                                                                                                                                                                                                                                 | Image: Instance         Image: Imag | [AUXOUTTEN]     [AUXOUTZEN]     [JSFKEN]     [ISFKEN]     [BIASGEN]     [BIASGEN]     [RMMEN]     [MIXEN]     [MIXEN]     [RMACEN] Right Channel DAC Enable     [LDACEN] Left Channel DAC Enable                                                                                                                           |  |

Figure 8: DEVICE CONTROL PANEL – BOARD SETTINGS

#### 7.3 Command Interface

This selects options for the control bus to the daughter card device. Normally, this selection is automatic and these settings should not be changed unless there is a specific goal to work with the command interface.

The listed options set up the motherboard and device on the daughter card to work together in the indicated mode. Additionally, the speed of the I2C clock can be altered.

### 7.4 External Control

In addition to the built-in interfaces, an external command interface control can be selected. In this case, control to and from the daughter card is via the CONT. PORT, Connector J24. Bidirectional level shifters are used to connect the daughter card to this port instead of to the internal port provided on the motherboard.

Coupled with the External Control is the ability to set the MODE pin on the NAU8822 device to high or low. This feature is needed to set the control mode in the NAU8822 device as described in the NAU8822 device design guide.

When using the CONT. PORT interface, an additional option exists to set the voltage used by the level shifter. This is changed by the jumper on Connector J23. Pin #1 of this connector is indicated by a square symbol on the PCB silkscreen.

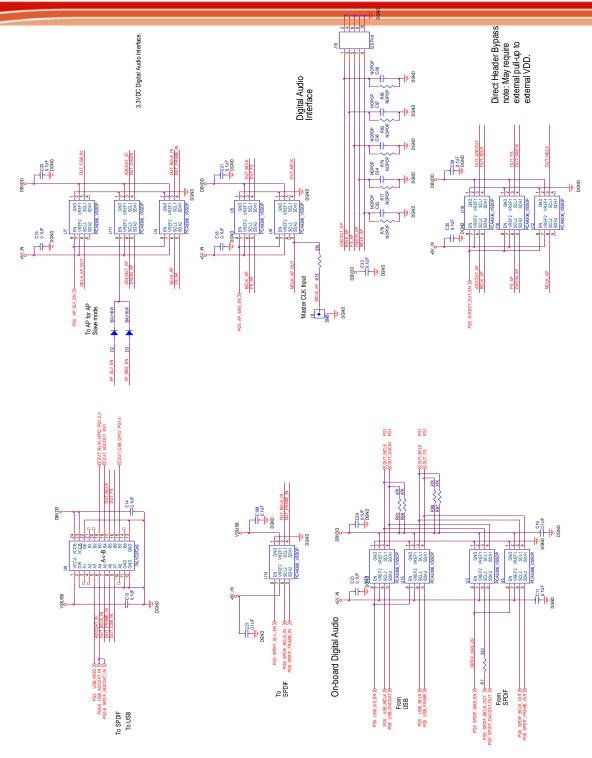

#### 7.5 I2S Signal Connection

The I2S path is the serial data path for audio the digital audio signal to and from the device on the daughter card. This feature is automatically handled, and should be changed only when specific work is being done with the I2S bus.

#### 7.5.1 Digital Audio Reset

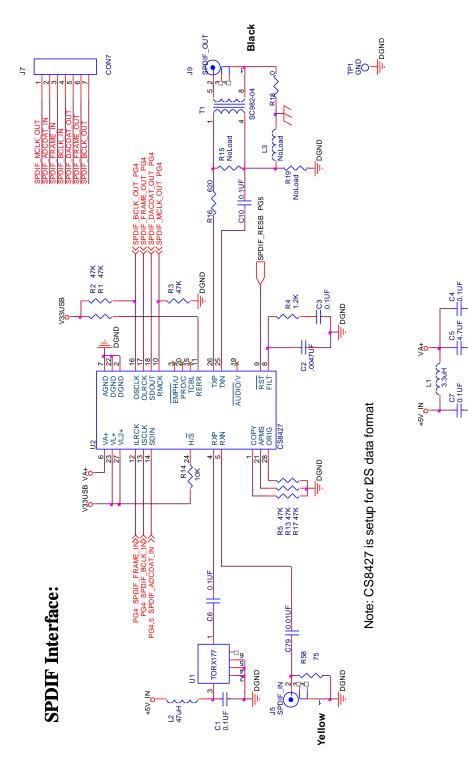

A SPDIF controller chip is included on the motherboard for coupling audio to and from the device on the daughter card using I2S serial data. Selecting this option will reset the SPDIF controller.

#### 7.5.2 I2S Master

The motherboard can be configured as the I2S Master or I2S Slave, but not both at the same time. In most applications, the motherboard will be the I2S Master. There are several options for the signal source in I2S Master Mode.

#### 7.5.3 On-Board USB

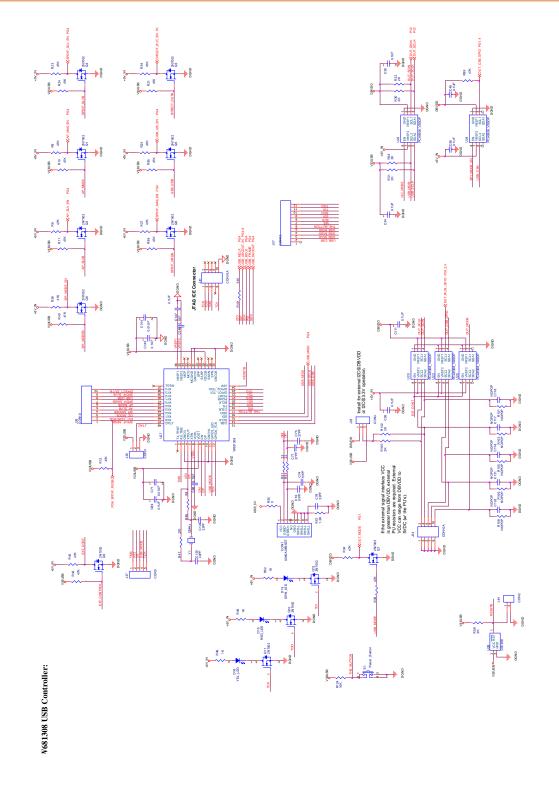

When audio is streamed from the USB host (typically a PC computer), the USB controller device on the motherboard is configured by this selection to be the I2S Master. When selecting USB audio in the Demo Panel, this selection is made automatically.

It should be noted that the built-in USB controller supports only a monophonic data stream. In the Demo Panel configuration, this same audio stream is output to both the left and right channels. Also, the USB mode does NOT support streaming of audio from the daughter card to the PC.

#### 7.5.4 Audio Precision I2S Master

This control is for when I2S audio is streamed from an external master source connected to the I2S\_PORT, Connector J15. Bi-directional level shifters are selected by this option to connect the daughter card to this port instead of to the internal port provided on the motherboard. External equipment, such as an Audio Precision analyzer must be configured to be the I2S master.

#### 7.5.5 Digital Audio Master

This control is for when I2S audio is streamed from the SPDIF controller included on the motherboard. Bi-directional level shifters are selected by this option to connect the daughter card to the SPDIF controller, instead of to the USB I2S port also provided on the motherboard. When selecting SPDIF audio in the Demo Panel, this selection is made automatically.

# ηυνοτοη

#### 7.5.6 I2S Slave

The motherboard can be configured as the I2S Master or I2S Slave, but not both at the same time. In most applications, the motherboard will be the I2S Master. This section controls options for the audio signal source in I2S slave mode.

#### 7.5.7 Audio Precision Slave Mode

This control is for when I2S audio is streamed to an external slave device connected to the I2S\_PORT, Connector J15. Bi-directional level shifters are selected by this option to connect the daughter card to this port instead of to the internal port provided on the motherboard. External equipment, such as an Audio Precision analyzer must be configured to be the I2S slave.

#### 7.5.8 Digital Audio Slave

This control is for when I2S audio is streamed to the SPDIF controller included on the motherboard. Bi-directional level shifters are selected by this option to connect the daughter card to the SPDIF controller, instead of to the USB I2S port also provided on the motherboard.

At the present time, the GUI Application software does not implement the ability for the SPDIF controller to stream audio out from SPDIF\_OUT, Connector J9.

#### 7.5.9 Direct Digital Audio Interface Header Enable

This control connects the I2S port on the daughter card device directly to the I2S\_PORT header Connector J15, but does not configure the daughter card device I2S direction. The daughter card device must be configured separately. Bi-directional level shifters are selected by this option to connect the daughter card to the J15 header connector, and not to any of the I2S devices on the motherboard.

## 8 Power Management

This panel of controls gives direct access to the various power management bits available in the NAU8822 device. Control of these bits is normally automatic. These bit controls are made available here for convenient manipulation and evaluation of the power control features.

The function of each of these control bits is explained in detail in the NAU8822 device Design Guide documentation. The names for each control in this panel match the names given to specific control bits in the NAU8822 control registers. The description and function for each of these bits can be found (most easily by doing a text string search) in the Details of Register Operation appendix portion of the NAU8822 device Design Guide.

Figure 9: DEVICE CONTROL PANEL – POWER MANAGEMENT

## 9 Input Path Control Panel

This Control Tab gives access to the various controls and settings for the analog audio input routing, power management, and gain blocks up to, but not including, the ADC converters. Control of these bits is normally automatic when using the Demo Panel. These bit controls are provided here for convenient manipulation and evaluation of the input path features and settings.

The function of each of these control bits is explained in detail in the NAU8822 device Design Guide documentation. The names for each control in this panel match the names given to specific control bits in the NAU8822 control registers. The description and function for each of these bits can be found (most easily by doing a text string search) in the Details of Register Operation appendix portion of the NAU8822 device Design Guide. It can also be helpful to switch to the Path View tab to better see how each of these controls affects the device settings and routing.

| 🛞 Nuvoton Audio Codec 🛛 8822 Demo                                                                                                                                                                                                                                                                                                              |                                                                                                                                                               |                                                                                                                                                                                                                                                         |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Device Mode Config Help                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                               |                                                                                                                                                                                                                                                         |  |

| Demo   Path View   Device Control Input Path   ADC/Filter                                                                                                                                                                                                                                                                                      | ring   Equalizer   Input Limiter/ALC   DAC/PLL/Dig Audio   Output P                                                                                           | ath   Register Map   Script                                                                                                                                                                                                                             |  |

| Power Management     [LPGAEN] Left Channel PGA Enable     [RPGAEN] Right Channel PGA Enable                                                                                                                                                                                                                                                    | Power Management                                                                                                                                              | Power Management<br>[ [LBSTEN] LADC Mix/Boost stage Enable<br>[ [RBSTEN] R ADC Mix/Boost stage Enable                                                                                                                                                   |  |

| Input Control<br>[LMICPLPGA] LMICP to L PGA Positive Input<br>[LMICNLPGA] LMICP to L PGA Negative Input<br>[LLINLPGA] LLIN to L PGA Positive Input<br>[IMICPRPGA] RMICP to R PGA Positive Input<br>[RMICNRPGA] RMICN to R PGA Positive Input                                                                                                   | MicroPhone Bias Volkage Control<br>[MICBIASM] MIC BIAS Mode                                                                                                   | Left ADC Boost<br>[LPGABST] L PGA Boost (+20dB over 0dB)<br>[LAUXBSTGAIN] LAUXIN Gain      ① 0.0dB<br>[LPGABSTGAIN] LUN Gain      ⑦ Path Disable<br>Right ADC Boost<br>[RPGABST] R PGA Boost (+20dB over 0dB)<br>[RAUXBSTGAIN] RAUXIN Gain      ⑦ 0.0dB |  |

| Left Input PGA Gain<br>[LPGAGAIN] L PGA Volume Setting ①0.0dB<br>「 [LPGAMT] L PGA Mute<br>「 [LPGAZC] L PGA Zero Cross<br>「 [LPGAU] PGA Volume Update bit<br>Right Input PGA Gain<br>[RPGAGAIN] R PGA Volume Setting ②0.0dB<br>「 [RPGAMT] R PGA Mute<br>「 [RPGAMT] R PGA Mute<br>「 [RPGAZC] R PGA Zero Cross<br>「 [RPGAU] PGA Volume Update bit | ALC Control<br>[ALCEN] ALC Select ALC Off<br>"When ALC is enabled, PGA volumes are controlled<br>automatically, and L,RPGAGAIN bits should not be<br>used. ** | [RPGABSTGAIN] RLIN Gain 🗘 Path Disable                                                                                                                                                                                                                  |  |

|                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                               |                                                                                                                                                                                                                                                         |  |

Figure 10: INPUT PATH CONTROL PANEL

#### 9.1 Microphone Bias

This section also provides control over the microphone bias circuit. This function provides lownoise DC power from the MICBIAS output pin that is normally used to power one or more external microphones. The description and function for each of these bits can be found (most easily by doing a text string search) in the functional descriptions, and also, the Detailed Register Map in the NAU8822 device Design Guide.

## **10 ADC/Filtering Control Panel**

This Control Tab gives access to the various controls and settings in the ADC converter blocks. Controls are also included here for the digital high pass filter, digital notch filter, and gain options associated with the ADC function.

Control of these bits is normally automatic when using the Demo Panel. These controls are provided in this panel for convenient manipulation and evaluation of the ADC section features and signal processing settings.

The function of each of these control bits is explained in detail in the NAU8822 device Design Guide documentation. The names for each control in this panel match the names given to specific control bits in the NAU8822 control registers. The description and function for each of these bits can be found (most easily by doing a text string search) in the Details of Register Operation appendix portion of the NAU8822 device Design Guide. It can also be helpful to switch to the Path View tab to better see how each of these controls affects the device settings and routing.

| 🗱 Nuvoton Audio Codec 🛛 |                                                                                                                                                                                                                                                                                                                                |  |  |  |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|